关键词:阻塞赋值,非阻塞赋值,并行

过程性赋值是在 initial 或 always 语句块里的赋值,赋值对象是寄存器、整数、实数等类型。

这些变量在被赋值后,其值将保持不变,直到重新被赋予新值。

连续性赋值总是处于激活状态,任何操作数的改变都会影响表达式的结果;过程赋值只有在语句执行的时候,才会起作用。这是连续性赋值与过程性赋值的区别。

Verilog 过程赋值包括 2 种语句:阻塞赋值与非阻塞赋值。

阻塞赋值

阻……继续阅读 »

2年前 (2022-07-27) 259浏览 0评论

0个赞

Verilog 具有很强的电路描述与建模能力,能从多个层次对数字系统进行描述和建模。因此,在简化硬件设计任务、提高设计效率与可靠性、语言易读性、层次化和结构化设计等方面展现了强大的生命力与潜力。

发展历史

1983 年,Verilog 最初由 Gateway Design Automation 公司(GDA)的 Phil Moorby 创建,作为内部仿真器的语言,主要用于逻辑建模和仿真验证,被广泛使用。

19……继续阅读 »

2年前 (2022-07-26) 250浏览 0评论

0个赞

关键词:任务

任务与函数的区别

和函数一样,任务(task)可以用来描述共同的代码段,并在模块内任意位置被调用,让代码更加的直观易读。函数一般用于组合逻辑的各种转换和计算,而任务更像一个过程,不仅能完成函数的功能,还可以包含时序控制逻辑。下面对任务与函数的区别进行概括:

比较点

函数

任务

输入

函数至少有一个输入,端口声明不能包含 inout 型

任务可以没有或者有多个输入,且端口声明可以为 in……继续阅读 »

2年前 (2022-07-23) 343浏览 0评论

0个赞

关键词: defparam,参数,例化,ram

当一个模块被另一个模块引用例化时,高层模块可以对低层模块的参数值进行改写。这样就允许在编译时将不同的参数传递给多个相同名字的模块,而不用单独为只有参数不同的多个模块再新建文件。

参数覆盖有 2 种方式:1)使用关键字 defparam,2)带参数值模块例化。

defparam 语句

可以用关键字 defparam 通过模块层次调用的方法,来改写低层次模块的参数值……继续阅读 »

2年前 (2022-07-21) 420浏览 0评论

0个赞

表达式

表达式由操作符和操作数构成,其目的是根据操作符的意义得到一个计算结果。表达式可以在出现数值的任何地方使用。例如:

实例

a^b ; //a与b进行异或操作

address[9:0] + 10’b1 ; //地址累加

flag1 && flag2 ; //逻辑与操作

操作……继续阅读 »

2年前 (2022-07-21) 217浏览 0评论

0个赞

以反引号 ` 开始的某些标识符是 Verilog 系统编译指令。

编译指令为 Verilog 代码的撰写、编译、调试等提供了极大的便利。

下面介绍下完整的 8 种编译指令,其中前 4 种使用频率较高。

`define, `undef

在编译阶段,`define 用于文本替换,类似于 C 语言中的 #define。

一旦 `define 指令被编译,其在整个编译过程中都会有效。例如,在一个文件中定义:

`define……继续阅读 »

2年前 (2022-07-20) 179浏览 0评论

0个赞

关键词:时延, 惯性时延

连续赋值延时语句中的延时,用于控制任意操作数发生变化到语句左端赋予新值之间的时间延时。

时延一般是不可综合的。

寄存器的时延也是可以控制的,这部分在时序控制里加以说明。

连续赋值时延一般可分为普通赋值时延、隐式时延、声明时延。

下面 3 个例子实现的功能是等效的,分别对应 3 种不同连续赋值时延的写法。

//普通时延,A&B计算结果延时10个时间单位赋值给Z

wire Z, ……继续阅读 »

2年前 (2022-07-18) 309浏览 0评论

0个赞

关键词:时延控制,事件触发,边沿触发,电平触发

Verilog 提供了 2 大类时序控制方法:时延控制和事件控制。事件控制主要分为边沿触发事件控制与电平敏感事件控制。

时延控制

基于时延的时序控制出现在表达式中,它指定了语句从开始执行到执行完毕之间的时间间隔。

时延可以是数字、标识符或者表达式。

根据在表达式中的位置差异,时延控制又可以分为常规时延与内嵌时延。

常规时延

遇到常规延时时,该语句需要等待一定时……继续阅读 »

2年前 (2022-07-18) 206浏览 0评论

0个赞

格式

Verilog 是区分大小写的。

格式自由,可以在一行内编写,也可跨多行编写。

每个语句必须以分号为结束符。空白符(换行、制表、空格)都没有实际的意义,在编译阶段可忽略。例如下面两中编程方式都是等效的。

不换行(不推荐)

实例

wire [1:0] results ;assign results = (a == 1’b0) ? 2’b……继续阅读 »

2年前 (2022-07-18) 415浏览 0评论

0个赞

设计方法

Verilog 的设计多采用自上而下的设计方法(top-down)。即先定义顶层模块功能,进而分析要构成顶层模块的必要子模块;然后进一步对各个模块进行分解、设计,直到到达无法进一步分解的底层功能块。这样,可以把一个较大的系统,细化成多个小系统,从时间、工作量上分配给更多的人员去设计,从而提高了设计速度,缩短了开发周期。

设计流程

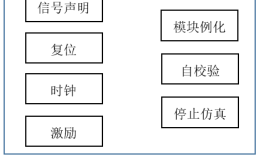

Verilog 的设计流程,一般包括以下几个步骤:

需求分析

工作……继续阅读 »

2年前 (2022-07-17) 303浏览 0评论

0个赞

关键词:deassign,force,release

过程连续赋值是过程赋值的一种。这种赋值语句能够替换其他所有 wire 或 reg 的赋值,改写了 wire 或 reg 型变量的当前值。

与过程赋值不同的是,过程连续赋值的表达式能被连续的驱动到 wire 或 reg 型变量中,即过程连续赋值发生作用时,右端表达式中任意操作数的变化都会引起过程连续赋值语句的重新执行。

过程连续性赋值主要有 2 种,assig……继续阅读 »

2年前 (2022-07-16) 228浏览 0评论

0个赞

关键词:assign, 全加器

连续赋值语句是 Verilog 数据流建模的基本语句,用于对 wire 型变量进行赋值。:

格式如下

assign LHS_target = RHS_expression ;

LHS(left hand side) 指赋值操作的左侧,RHS(right hand side)指赋值操作的右侧。

assign 为关键词,任何已经声明 wire 变量的连续赋值语句都是以 ass……继续阅读 »

2年前 (2022-07-16) 295浏览 0评论

0个赞

关键词:顺序块,并行块,嵌套块,命名块,disable

Verilog 语句块提供了将两条或更多条语句组成语法结构上相当于一条一句的机制。主要包括两种类型:顺序块和并行块。

顺序块

顺序块用关键字 begin 和 end 来表示。

顺序块中的语句是一条条执行的。当然,非阻塞赋值除外。

顺序块中每条语句的时延总是与其前面语句执行的时间相关。

在本节之前的仿真中,initial 块中的阻塞赋值,都是顺序块的实例……继续阅读 »

2年前 (2022-07-16) 213浏览 0评论

0个赞

关键字:例化,generate,全加器,层次访问

在一个模块中引用另一个模块,对其端口进行相关连接,叫做模块例化。模块例化建立了描述的层次。信号端口可以通过位置或名称关联,端口连接也必须遵循一些规则。

命名端口连接

这种方法将需要例化的模块端口与外部信号按照其名字进行连接,端口顺序随意,可以与引用 module 的声明端口顺序不一致,只要保证端口名字与外部信号匹配即可。

下面是例化一次 1bit 全加器的例子:

实……继续阅读 »

2年前 (2022-06-30) 228浏览 0评论

0个赞

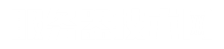

关键词:状态机,售卖机

有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。状态机不仅是一种电路的描述工具,而且也是一种思想方法,在电路设计的系统级和 RTL 级有着广泛的应用。

状态机类型

Verilog 中状态机主要用于同步时序逻辑的设计,能够在有限个状态之间按一定要求和规律切换时序电路的状态。状态的切换方向不但取决于各……继续阅读 »

2年前 (2022-06-28) 387浏览 0评论

0个赞

串行 FIR 滤波器设计

设计说明

设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR 滤波器后,高频信号 7.5MHz 被滤除,只保留 250KMHz 的信号。

输入频率: 7.5MHz 和 250KHz

采样频率: 50MHz

阻带: 1MHz-6MHz

阶数: 15 (N=15)

……继续阅读 »

2年前 (2022-06-27) 173浏览 0评论

0个赞

关键词:if,选择器

条件语句

条件(if)语句用于控制执行语句要根据条件判断来确定是否执行。

条件语句用关键字 if 和 else 来声明,条件表达式必须在圆括号中。

条件语句使用结构说明如下:

if (condition1) true_statement1 ;

else if (condition2) true_statement2 ;

else if (condition3) ……继续阅读 »

2年前 (2022-06-27) 302浏览 0评论

0个赞

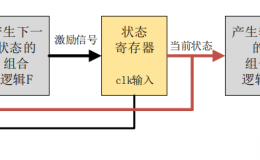

DDS 原理

DDS(直接频率合成)技术是根据奈奎斯特抽样定理及数字处理技术,把一系列的模拟信号进行不失真的抽样,将得到的数字信号存储在存储器中,并在时钟的控制下,通过数模转换,将数字量变成模拟信号的方法。

DDS 模块主要由相位累加器、查找表、DAC 转换器和低通滤波器组成,基本结构如下。

相位累加器,是 DDS 的核心组成部分,用于实现相位的累加,并输出相应的幅值。相位累加器由 M 位宽加法器和 M 位宽寄……继续阅读 »

2年前 (2022-06-23) 206浏览 0评论

0个赞

关键词:case,选择器

case 语句是一种多路条件分支的形式,可以解决 if 语句中有多个条件选项时使用不方便的问题。

case 语句

case 语句格式如下:

case(case_expr)

condition1 : true_statement1 ;

condition2 : true_statement2 ;

&he……继续阅读 »

2年前 (2022-06-19) 1008浏览 0评论

0个赞

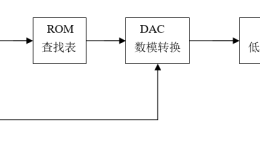

FFT(Fast Fourier Transform),快速傅立叶变换,是一种 DFT(离散傅里叶变换)的高效算法。在以时频变换分析为基础的数字处理方法中,有着不可替代的作用。

FFT 原理

公式推导

DFT 的运算公式为:

其中,

将离散傅里叶变换公式拆分成奇偶项,则前 N/2 个点可以表示为:

同理,后 N/2 个点可以表示为:

由此可知,后 N/2 个点的值完全可以通过计算前 N/2 个点时的中间过程……继续阅读 »

2年前 (2022-06-17) 256浏览 0评论

0个赞

关键词:testbench,仿真,文件读写

Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真。

毫不夸张的说,对于稍微复杂的 Verilog 设计,如果不进行仿真,即便是经验丰富的老手,99.9999% 以上的设计都不会正常的工作。不能说仿真比设计更加的重要,但是一般来说,仿真花费的时间会比设计花……继续阅读 »

2年前 (2022-06-16) 209浏览 0评论

0个赞

关键词:触发器,锁存器

Latch 的含义

锁存器(Latch),是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

当电平信号无效时,输出信号随输入信号变化,就像通过了缓冲器;当电平有效时,输出信号被锁存。激励信号的任何变化,都将直接引起锁存器输出状态的改变,很有可能会因为瞬态特性不稳定而产生振荡现象。

锁存器示意图如下:

触……继续阅读 »

2年前 (2022-06-16) 196浏览 0评论

0个赞

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。

FIR 滤波器具有严格的线性相频特性,同时其单位响应是有限长的,因而是稳定的系统,在数字通信、图像处理等领域都有着广泛的应用。

FIR 滤波器原理

FIR 滤波器是有限长单位冲击响应滤波器。直接型结构如下:

FIR 滤波器本质上就是输入信号与单位冲击响应函数的卷积,表达式如下:

FIR 滤波器有如……继续阅读 »

2年前 (2022-06-16) 195浏览 0评论

0个赞

Verilog 最常用的 2 种数据类型就是线网(wire)与寄存器(reg),其余类型可以理解为这两种数据类型的扩展或辅助。

线网(wire)

wire 类型表示硬件单元之间的物理连线,由其连接的器件输出端连续驱动。如果没有驱动元件连接到 wire 型变量,缺省值一般为 “Z”。举例如下:

实例

wire interrupt ;

wire flag1, flag……继续阅读 »

2年前 (2022-06-13) 186浏览 0评论

0个赞

关键词:流水线,乘法器

硬件描述语言的一个突出优点就是指令执行的并行性。多条语句能够在相同时钟周期内并行处理多个信号数据。

但是当数据串行输入时,指令执行的并行性并不能体现出其优势。而且很多时候有些计算并不能在一个或两个时钟周期内执行完毕,如果每次输入的串行数据都需要等待上一次计算执行完毕后才能开启下一次的计算,那效率是相当低的。流水线就是解决多周期下串行数据计算效率低的问题。

流水线

流水线的基本思想是:把一个重……继续阅读 »

2年前 (2022-06-12) 158浏览 0评论

0个赞

关键词:模块,端口,双向端口,PAD

结构建模方式有 3 类描述语句: Gate(门级)例化语句,UDP (用户定义原语)例化语句和 module (模块) 例化语句。本次主要讲述使用最多的模块级例化语句。

模块

模块是 Verilog 中基本单元的定义形式,是与外界交互的接口。

模块格式定义如下:

module module_name

#(parameter_list)

(port_list) ;

……继续阅读 »

2年前 (2022-06-10) 220浏览 0评论

0个赞

关键字:竞争,冒险,书写规范

产生原因

数字电路中,信号传输与状态变换时都会有一定的延时。

在组合逻辑电路中,不同路径的输入信号变化传输到同一点门级电路时,在时间上有先有后,这种先后所形成的时间差称为竞争(Competition)。

由于竞争的存在,输出信号需要经过一段时间才能达到期望状态,过渡时间内可能产生瞬间的错误输出,例如尖峰脉冲。这种现象被称为冒险(Hazard)。

竞争不一定有冒险,但冒险一定会有竞争……继续阅读 »

2年前 (2022-06-09) 172浏览 0评论

0个赞

学习 Verilog 做仿真时,可选择不同仿真环境。FPGA 开发环境有 Xilinx 公司的 ISE(目前已停止更新),VIVADO;因特尔公司的 Quartus II;ASIC 开发环境有 Synopsys 公司的 VCS ;很多人也在用 Icarus Verilog 和 GTKwave 的方法,更加的轻便。

虽然 ISE 或者 Quartus II 都会自带仿真器,但功能还是有欠缺。所以,这里介绍下 Quar……继续阅读 »

2年前 (2022-06-08) 193浏览 0评论

0个赞

前言

本教程主要讲述 Verilog 完成数字 IC 设计(数字集成电路设计,Digital Integrated Circuit Design) 时涉及的一些知识,更加注重数字电路安全、稳定、方便的实现。将该教程理解为 《Verilog 教程》的高级篇,也再适当不过。

内容主要包括:底层(1章 门级建模、2章 用户自定义原语 UDP、9章 逻辑综合)、时序(3章 时序分析)、优化(4章 同步与异步、5章 复位与时钟……继续阅读 »

2年前 (2022-06-04) 165浏览 0评论

0个赞

除法器原理(定点)

和十进制除法类似,计算 27 除以 5 的过程如下所示:

除法运算过程如下:

(1) 取被除数的高几位数据,位宽和除数相同(实例中是 3bit 数据)。

(2) 将被除数高位数据与除数作比较,如果前者不小于后者,则可得到对应位的商为 1,两者做差得到第一步的余数;否则得到对应的商为 0,将前者直接作为余数。

(3) 将上一步中的余数与被除数剩余最高位 1bit 数据拼接成新的数据,……继续阅读 »

2年前 (2022-06-02) 227浏览 0评论

0个赞